काठमाडौं ।

ह्वावेको पछिल्लो सर्भर चिप ‘कुनपेङ ९३०’ टीएसएमसीको ५एनएम आर्किटेक्चरमा निर्माण गरिएको रिपोर्ट गरिएको छ। यो जानकारी(निष्कर्ष) कुर्नालसाल्ट्सले प्रक्रियाको बारेमा साझा गरेको टियरडाउन भिडियोमार्फत खुलासा गरिएको बताइएको छ। नयाँ चिपले यसको पूर्ववर्ती भन्दा लगभग २× पर्फर्मेन्स जम्प प्रदान गर्ने उल्लेख गरिएको छ। यद्यपि यो चिप अझै पनि इन्टेल र एएमडी प्रस्तावहरूको पछिल्लो पुस्ताबाट केही पुस्ता टाढा रहेको जनाइएको छ।

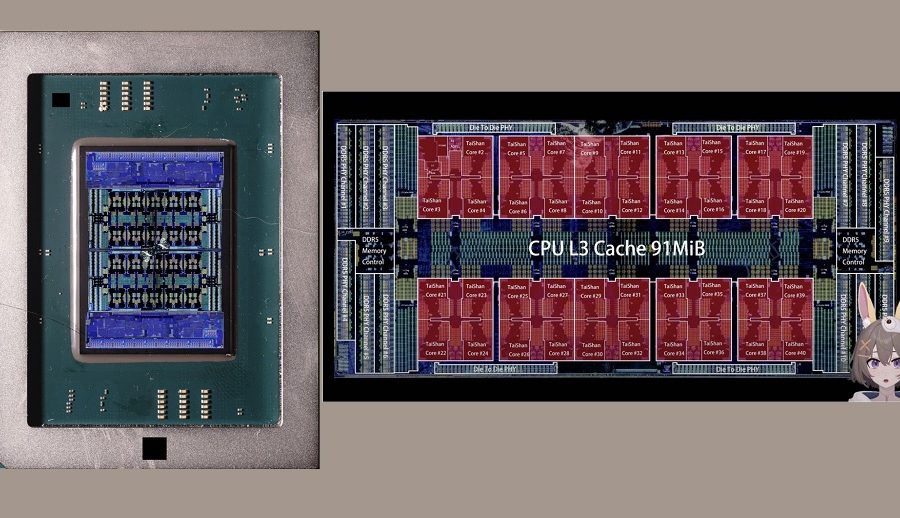

कुनपेङ ९३० मा टीएसएमसीको एन५ प्रोसेसमा फ्याब गरिएको सीपीयू रहेको छ भने आई÷ओ डाई सम्भवतः एसएमआईसीको १४एनएम प्रोसेस भएको अनुमान गरिएको छ। ७७.५एमएम × ५८.०एमएम चिपमा माउन्ट ताइशान सीपीयू आर्किटेक्चर सहितको डुअल–सकेट मदरबोर्ड रहेको छ जसमा प्रत्येक सीपीयू डाईमा १० सीपीयू क्लस्टरहरू छन्। ती प्रत्येक क्लस्टरले २ सीपीयू कोरहरू एकीकृत गर्दछन् र कुल गणना ८० कोरमा ल्याउने जनाइएको छ।

यसको अतिरिक्त, कुनपेङ ९३० भित्र प्रत्येक डाईमा ९१एमबी एल३ क्यास र २एमबी एल२ क्यास सपोर्ट रहेको छ। चिपले १६–च्यानल मेमोरी जडानको साथ ९६ पीसीआई लेनहरू पनि ल्याएको जीएसएमएरिनाले रिपोर्ट गरेको छ।

प्रकाशित: १३ भाद्र २०८२, शुक्रबार